WIZnet 發布世界上第一款IOP(網絡卸載處理器)W7500 芯片,內嵌 ARM Cortex-M0 及 硬件TCP/IP協議棧,目標進軍物聯網市場。

W7500 及其測試板 — “WIZWiki-W7500〞 設計用於 ARM mbed平台及 Arduino。

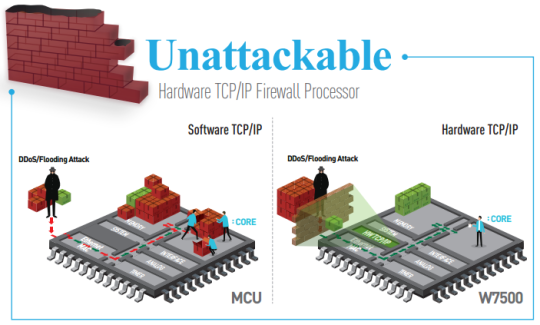

W7500 是一款單芯片的網絡卸載處理器(IOP)。它不僅內嵌 128KB Flash 的ARM Coretex-M0內核,還包含了全硬件TCP/IP協議棧內核。從而,適用於各類嵌入式應用平台。特別是在物聯網領域。

其集成了以太網 MAC 的 TCP/IP 協議棧內核,支持 TCP, UDP, IPv4, ICMP, ARP, IGMP 以及 PPPoE 協議,久經市場考驗,並得到廣泛認可。W7500 特別適用於應用中需要網絡連接的用戶。

特點

ARM Cortex-M0

◾最大時鐘頻率 48MHz

全硬件TCP/IP核

◾8個socket

◾每個socket擁有最大32KBSRAM

◾MII(介質無關接口)

內存

◾Flash:128KB

◾SRAM:16KB到48KB(如32KB socket 緩存已用,最小可用16KB,如果socket緩存未用,最大可用48KB)

◾用於Boot程序存儲的ROM:6KB

時鐘,復位及供給管理

◾POR(上電復位)

◾穩壓器:3.3V到1.5V

◾8 到 24 MHz 的外部晶體振蕩器

◾內部內部 8 MHz 的阻容振蕩器

◾用於 CPU 時鐘的鎖相環

ADC

◾12bit,8ch,1Msps

DMA

◾6 路 DMA 控制器

◾外設: UARTs, SPIs

GPIO

◾53 I/Os (16 IO x 3ea, 5 IO x 1ea)

調試方式

◾串行調試 (SWD)

定時器/PWM

◾看門狗*1 (32位減法計數器)

◾計時器*4 (32位或16位減法計數器)

◾PWM*8 (帶有6位可編程預分頻器的32計數器/定時器)